Ein neues asynchrones JK-Flipflop

Auch zu diesem Thema haben mir gegenüber 'Experten' in Diskussionsforen schon Ihre Ablehnung sehr heftig zum

Ausdruck gebracht und ihre Unkenntnis sowie Lernunwilligkeit bestätigt. Da sie so etwas in der Schule oder auf der Uni nicht gelehrt

bekamen, es also nicht kannten, kann es nach deren Meinung so etwas auch nicht geben. Ich bin mir nicht sicher, ob

vielleicht ein Diskussionsgegner nur mal den Versuch unternahm, die Funktionsweise der Schaltung zu begreifen.

Das betrifft ganz sicher auch die deutschen und ganz besonders die englischen Wikipedia-Mitarbeiter.

Nur noch einmal zur Wiederholung die Eigenschaften eines JK-Flipflops:

- Ein 1-Signal am J-Eingang setzt das JK-Flipflop

- Ein 1 Signal am K-Eingang setzt das JK-Flipflop zurück

- Ein 1-Signal an beiden Eingängen verändert den Zustand. War das JK-Flipflop gesetzt, wird es dadurch zurückgesetzt und umgekehrt. Man spricht hierbei von "toggeln".

Im folgenden wird nun der Aufbau eines JK-Flipflops beschrieben, das kein separates Taktsignal benötigt.

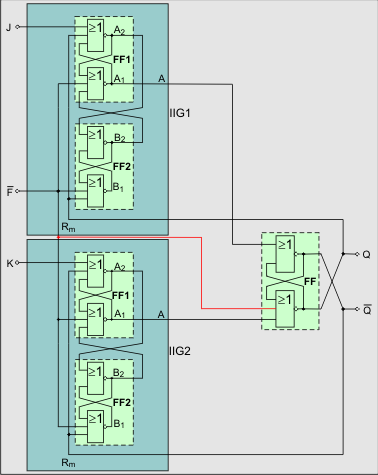

Dazu wird ein RS-Flipflop verwendet, dem vor jeden Eingang das im vorigen Kapitel 'Ideales Impulsglied' abgeleitete ideale Impulsglied geschaltet

ist. Die Ausgänge dieses RS-Flipflops sind die Signale für die Rückmeldung, die jetzt nur noch an die Rm-Eingänge

der idealen Impulsglieder zurückgeführt werden müssen.

Der Aufbau eines nichtgetakteten (asynchronen) JK-Flipflop ist in Abb. 5 dargestellt.

Werden beide Eingänge J und K miteinander verbunden, erhält man einen Frequenzteiler (T-Flipflop).

Auch hier sei noch einmal darauf hingewiesen, dass der gesamte Aufbau mit NAND-Gattern erfolgen kann. Das RS-Flipflop am Ausgang wird immer beide Ausgangssignale negiert zueinander ausgeben. Deshalb kann hier wieder Q und /Q verwendet werden.

Abb. 5 Nicht getaktetes asynchrones JK-Flipflop

Dieses JK Flipflop ist nicht (separat) taktgesteuert und arbeitet damit asynchron.

Das Besondere dabei ist, dass die Eingänge J und K flankengetriggert sind. Das bedeutet, dass das Flipflop in die jeweilige Ausgangslage kippt,

wenn am entsprechenden Eingang eine Signaländerung von 0 nach 1 erfolgt.

Dabei spielt es keine Rolle ob am anderen Eingang 0- oder

1-Signal (stabil) anliegt.

Grund dafür sind die Eigenschaften des vorgestellten idealen Impulsgliedes.

Erreicht werden diese Eigenschaften durch die Nutzung der bisher missachteten/verbotenen Eingangsbelegung R=S=1.

J - Setz-Eingang

K - Rücksetz-Eingang

Q - Ausgang

Die zusätzlich rot dargestellte Verbindung wurde von Stefan Dumler in seinem Testbericht zum JK-FF vorgeschlagen, um nach einer Freigabe einen definierten Anfangszustand zu erreichen.

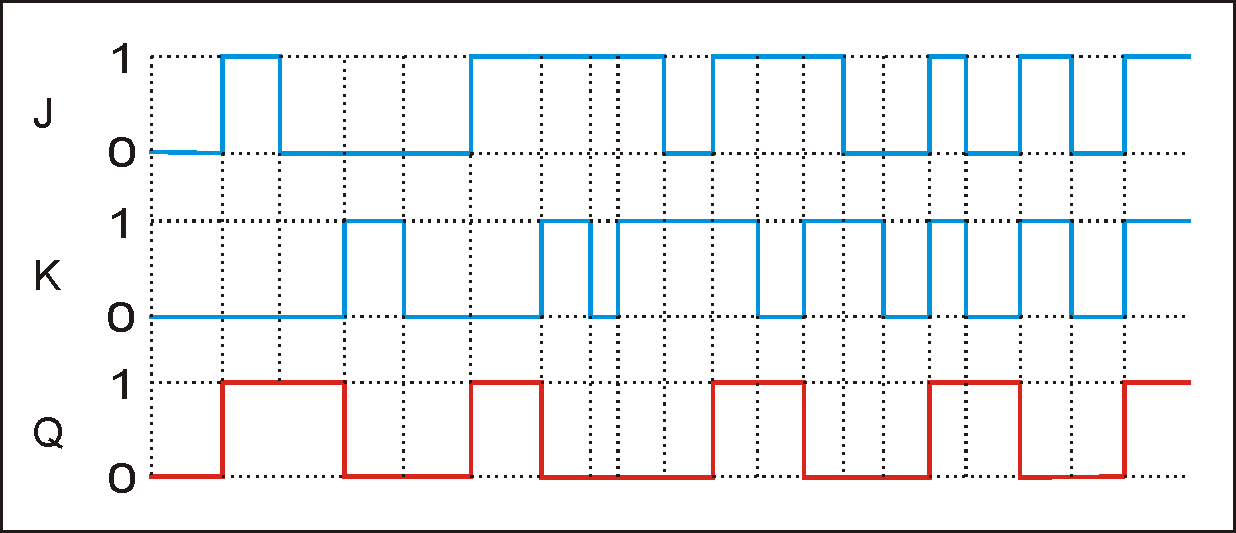

Abb. 6 Zugehöriges Impulsdiagramm

Ergänzung:

Diese Schaltung wurde bereits in den Jahren 1981/82 entwickelt. Ich wurde im Juli 2011 darüber informiert, dass im Jahr 2001 noch einmal

eine änliche Schaltung mit der im Prinzip gleichen Funktionsweise entwickelt wurde.

Das Wesentliche ist auch dabei die

sinnvolle Nutzung der R=S=1-Belegung (NOR) eines RS-Flipflops.

Die Schaltung ist in einem Forum zu finden.